Unlock your full potential by mastering the most common Electronic Materials and Devices interview questions. This blog offers a deep dive into the critical topics, ensuring you’re not only prepared to answer but to excel. With these insights, you’ll approach your interview with clarity and confidence.

Questions Asked in Electronic Materials and Devices Interview

Q 1. Explain the differences between n-type and p-type semiconductors.

The difference between n-type and p-type semiconductors lies in the type of majority charge carriers they possess. This difference arises from the process of doping, where we intentionally introduce impurity atoms into an intrinsic (pure) semiconductor like silicon.

n-type semiconductors are created by doping silicon with a pentavalent impurity (e.g., phosphorus, arsenic, or antimony). These impurities have five valence electrons, and four of them bond with the silicon atoms, leaving one extra electron free to move around. These free electrons become the majority charge carriers, while the positive ‘holes’ (the absence of an electron) become the minority carriers. Think of it like adding extra marbles to a box – the marbles are the electrons.

p-type semiconductors, conversely, are formed by doping silicon with a trivalent impurity (e.g., boron, gallium, or indium). These impurities have three valence electrons, creating a ‘hole’ – an empty space where an electron should be – in the silicon lattice. These holes act as the majority charge carriers, accepting electrons from neighboring atoms. The few free electrons present become the minority carriers. In our marble analogy, we’ve removed some marbles, creating empty spaces (holes).

The presence of these majority carriers drastically alters the electrical conductivity of the semiconductor. N-type materials have a negative charge and p-type materials have a positive charge, allowing for the creation of p-n junctions, the foundation of many electronic devices like diodes and transistors.

Q 2. Describe the process of silicon wafer fabrication.

Silicon wafer fabrication is a complex multi-step process crucial for creating integrated circuits. It begins with the production of high-purity silicon crystals from silicon dioxide (sand) through a process called the Czochralski (CZ) method. A large, single-crystal silicon ingot is grown from a molten silicon pool, carefully controlled for purity and crystallographic perfection.

This ingot is then sliced into thin circular wafers using diamond saws. These wafers are then polished to an extremely smooth, mirror-like surface to ensure uniformity and defect-free layers during subsequent processing.

The next crucial stage is photolithography. This involves using ultraviolet (UV) light to transfer a circuit pattern from a photomask onto the wafer’s surface coated with a photosensitive material (photoresist). This process defines where different materials will be deposited or etched. A series of lithographic steps, etching, and deposition create layers of different materials (like silicon dioxide, silicon nitride, polysilicon, and metals) to build the transistor structures and interconnect the devices.

Doping is integrated during specific steps to create the n-type and p-type regions needed for transistors and other components. After numerous cycles of photolithography, etching, and deposition, metallization steps interconnect all components to form a functional circuit. Finally, the wafer is tested and diced into individual chips, which are then packaged for use in electronic devices. The entire process requires extremely clean-room environments and precise control at each stage to guarantee high yields and performance.

Q 3. What are the key characteristics of a good dielectric material?

A good dielectric material is crucial in electronic devices as it acts as an insulator, preventing current flow while storing electrical energy in an electric field. Key characteristics include:

- High dielectric constant (k): A higher k value means the material can store more charge for a given voltage, leading to smaller capacitor sizes. Think of it as the material’s ability to ‘hold’ the electric field.

- Low dielectric loss (tan δ): This represents energy dissipation as heat in the dielectric when subjected to an electric field. Lower losses are crucial for efficiency and preventing overheating.

- High breakdown strength: The ability to withstand a high electric field before electrical breakdown occurs. This is vital to ensure the dielectric doesn’t fail under operating conditions.

- Good temperature stability: The dielectric properties should remain consistent across a wide range of temperatures to ensure reliable performance in various environments.

- Chemical inertness: The material should not react with other components in the device.

- Ease of processing: The material should be easy to deposit and pattern during fabrication.

Examples of commonly used dielectric materials include silicon dioxide (SiO2), silicon nitride (Si3N4), and various high-k dielectrics like hafnium oxide (HfO2) used in modern transistors to improve performance and reduce power consumption.

Q 4. Explain the working principle of a MOSFET.

The Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) is a fundamental building block of modern electronics. It acts as a switch controlled by an electric field. It consists of a channel region (typically silicon) sandwiched between two heavily doped regions called the source and drain. This channel is insulated from a gate electrode by a thin layer of dielectric material (usually silicon dioxide).

When a positive voltage is applied to the gate, it creates an electric field that attracts electrons to the channel in an n-type MOSFET (or holes in a p-type MOSFET), forming a conductive path between the source and drain. This allows current to flow. Removing the gate voltage, or applying a negative voltage, eliminates the conductive path, turning the transistor ‘off’.

This process effectively allows us to control the current flow between the source and drain by varying the voltage applied to the gate. This makes MOSFETs extremely versatile as switches and amplifiers, forming the backbone of integrated circuits like microprocessors and memory chips. Their low power consumption and high switching speed are key reasons for their widespread use.

Q 5. How does doping affect the conductivity of a semiconductor?

Doping significantly affects the conductivity of a semiconductor by altering the number of charge carriers (electrons or holes) available for current conduction. Intrinsic semiconductors have a relatively low conductivity because the number of charge carriers is limited to those thermally generated.

Doping increases conductivity by introducing impurity atoms into the semiconductor lattice. In n-type doping, the extra electrons from pentavalent impurities dramatically increase the number of free electrons available to carry current. Similarly, in p-type doping, the holes created by trivalent impurities become the majority carriers, increasing conductivity. The higher the doping concentration, the higher the conductivity becomes.

This control over conductivity is crucial in designing electronic devices. For instance, heavily doped regions are used to create low-resistance contacts, while lightly doped regions are used to control the flow of current in transistors. The precise control of doping concentration allows for fine-tuning of the electrical properties of semiconductors, essential for device performance.

Q 6. Discuss the different types of semiconductor junctions.

Semiconductor junctions are formed by joining regions of different conductivity types (n-type and p-type) within a single semiconductor material. The most common types include:

- p-n junction: The simplest and most fundamental type, formed by joining a p-type and an n-type semiconductor. It forms a depletion region near the junction, resulting in rectifying properties – allowing current flow in one direction and blocking it in the other (used in diodes).

- p-n-p and n-p-n junctions: These are the basis of bipolar junction transistors (BJTs). The middle region (n or p) is thin and controls current flow between the outer p and n regions.

- Metal-semiconductor junction (Schottky junction): Formed between a metal and a semiconductor, exhibiting rectifying behavior. These are used in Schottky diodes which are known for their fast switching speeds.

- Heterojunctions: These are junctions formed between two different semiconductor materials (e.g., GaAs and AlGaAs). This allows for the creation of devices with tailored band gaps and other properties useful for high-frequency and optoelectronic applications.

Understanding the characteristics of these junctions is essential for designing various electronic and optoelectronic devices. Each type exhibits unique electrical characteristics that influence their application in different circuit architectures.

Q 7. What are the challenges in miniaturizing electronic devices?

Miniaturizing electronic devices, while driving progress in computing power and efficiency, presents several challenges:

- Short channel effects (SCE): As transistors shrink, the control of the channel by the gate becomes less effective, leading to performance degradation and increased leakage current.

- Quantum mechanical effects: At the nanoscale, quantum tunneling becomes significant, allowing current leakage even when the transistor should be ‘off’. This consumes power and limits performance.

- Heat dissipation: Packing more transistors into smaller spaces leads to higher power densities, increasing the challenge of efficiently removing heat to prevent device failure.

- Lithographic limitations: Manufacturing smaller features requires more sophisticated and expensive lithographic techniques, reaching fundamental limitations in resolution.

- Material properties: Finding new materials with suitable properties at the nanoscale is crucial for overcoming limitations of current materials.

- Interconnect limitations: As devices become smaller, interconnects between them become more resistive, increasing signal delay and power consumption.

Addressing these challenges requires interdisciplinary efforts involving materials science, device physics, and fabrication technologies. Innovative approaches like new materials, novel device architectures, and advanced fabrication techniques are constantly being explored to continue the trend of miniaturization.

Q 8. Explain the concept of band gap engineering.

Band gap engineering is the process of manipulating the band gap of a semiconductor material to tailor its electronic properties for specific applications. Think of the band gap as an energy barrier electrons need to overcome to move from the valence band (where electrons are bound to atoms) to the conduction band (where they’re free to conduct electricity). By altering the band gap, we control the material’s conductivity, light absorption/emission characteristics, and other crucial properties.

This is achieved primarily through alloying—mixing different semiconductor materials—or by applying strain to the material lattice. For example, varying the ratio of gallium arsenide (GaAs) and aluminum arsenide (AlAs) allows for fine-tuning the band gap of the resulting AlxGa1-xAs alloy. A larger percentage of AlAs leads to a wider band gap and makes the material a better insulator; a higher percentage of GaAs narrows the gap, increasing conductivity. This precise control is essential in creating various optoelectronic devices such as lasers and LEDs, where the band gap determines the wavelength of light emitted.

In practice, band gap engineering is crucial for designing heterostructures, where layers of different semiconductors with varying band gaps are stacked together to create advanced devices. This is the foundation of many high-performance transistors, solar cells, and other semiconductor technologies.

Q 9. Describe various techniques for characterizing semiconductor materials.

Semiconductor characterization involves a suite of techniques to determine a material’s electrical, optical, and structural properties. These techniques are crucial for quality control and research & development.

- Electrical Characterization: This includes measuring resistivity (using four-point probe or van der Pauw method), carrier concentration (Hall effect measurement), and mobility (from Hall effect data).

- Optical Characterization: Techniques like UV-Vis spectroscopy measure light absorption and transmission to determine the band gap, while photoluminescence (PL) spectroscopy reveals information about radiative recombination processes within the material.

- Structural Characterization: X-ray diffraction (XRD) determines crystal structure and orientation, while scanning electron microscopy (SEM) and transmission electron microscopy (TEM) provide high-resolution images of the material’s microstructure, revealing defects and grain boundaries.

- Other Techniques: Deep-level transient spectroscopy (DLTS) reveals information about trap states within the band gap, while ellipsometry measures optical constants like refractive index and extinction coefficient.

Choosing the appropriate technique depends on the specific information needed and the material’s properties. For instance, if we’re designing a high-speed transistor, measuring carrier mobility is crucial. If developing a solar cell, determining the band gap and light absorption characteristics is essential.

Q 10. What are the different types of thin-film deposition techniques?

Thin-film deposition is a crucial step in fabricating many electronic devices. It involves creating thin layers of materials onto a substrate. Several techniques exist, each with its own advantages and disadvantages:

- Physical Vapor Deposition (PVD): This involves physically removing material from a source and depositing it onto a substrate. Examples include sputtering (using plasma to bombard a target material) and evaporation (heating a material in vacuum).

- Chemical Vapor Deposition (CVD): This uses chemical reactions in the gas phase to deposit a thin film. The reactants are introduced into a reaction chamber, where they decompose and react to form the desired film on the substrate. Different types of CVD exist, including atmospheric pressure CVD (APCVD), low-pressure CVD (LPCVD), and metal-organic CVD (MOCVD).

- Atomic Layer Deposition (ALD): This technique allows for highly precise control over film thickness at the atomic level. It involves sequential, self-limiting surface reactions, resulting in uniform and conformal coatings.

- Solution-based Deposition: Techniques such as spin coating, dip coating, and inkjet printing use liquid precursors to deposit films. These are often simpler and cheaper than PVD or CVD but may result in films with lower quality and less control over thickness uniformity.

The choice of deposition technique is determined by factors like material properties, desired film thickness and quality, cost, and scalability.

Q 11. How do you measure the resistivity of a semiconductor material?

Measuring the resistivity of a semiconductor material is crucial to understanding its conductivity. A common and relatively simple method is the four-point probe technique.

Four-Point Probe Method: This technique minimizes the effect of contact resistance. Four equally spaced probes are placed on the material’s surface. A current is passed through the outer two probes, and the voltage drop across the inner two probes is measured. Resistivity (ρ) is then calculated using the following formula:

ρ = (V/I) * 2πswhere V is the voltage, I is the current, and s is the spacing between the probes. This formula applies for a homogeneous, semi-infinite sample. For other geometries, correction factors are needed. For example, the van der Pauw method is used for irregularly shaped samples.

The accuracy of the measurement depends on several factors including probe spacing, probe contact resistance, and sample homogeneity. Proper calibration and careful measurement are essential for reliable results.

Q 12. Explain the concept of carrier mobility.

Carrier mobility (μ) describes how easily electrons or holes (charge carriers) move through a semiconductor material under the influence of an electric field. It’s essentially a measure of how fast the carriers can drift in response to the applied field. High mobility indicates that carriers can move easily, resulting in higher conductivity. Low mobility suggests that carriers are impeded by scattering mechanisms, reducing conductivity.

The mobility is influenced by several factors including:

- Temperature: Higher temperatures generally lead to lower mobility due to increased thermal vibrations of the lattice atoms, which scatter the carriers.

- Impurity concentration: High impurity concentrations lead to increased scattering from ionized impurities, decreasing mobility.

- Crystal defects: Defects in the crystal lattice scatter carriers, reducing mobility.

Mobility is usually calculated from Hall effect measurements, which involve measuring the voltage developed across a sample perpendicular to both the applied current and an external magnetic field. The Hall coefficient provides information about carrier concentration and type (electrons or holes), and together with the conductivity, the mobility can be calculated. Understanding mobility is crucial for designing high-performance transistors and other semiconductor devices where fast charge transport is essential.

Q 13. What are the limitations of Moore’s Law?

Moore’s Law, which predicted the doubling of transistors on a microchip roughly every two years, has been a driving force behind the semiconductor industry’s remarkable progress. However, its limitations are becoming increasingly apparent:

- Physical Limits: Transistors are approaching atomic-scale dimensions, where quantum effects become significant and further miniaturization becomes challenging. This leads to issues like leakage current and reduced control over transistor behavior.

- Power Consumption: Smaller transistors can lead to increased power density, resulting in excessive heat generation and requiring sophisticated cooling solutions. This increases both the cost and complexity of manufacturing.

- Cost of Manufacturing: The cost of fabrication facilities (fabs) is escalating rapidly as more advanced lithographic techniques are needed for finer feature sizes. The cost of research and development also increases continuously as we approach these physical limits.

- Material Limitations: Silicon, the dominant material in semiconductor technology, has inherent limitations, including lower electron mobility compared to some other materials.

The industry is exploring various strategies to overcome these limitations, including novel materials like graphene and other 2D materials, new device architectures (such as FinFETs and GAAFETs), and advanced packaging techniques. These strategies are crucial to continue advancing semiconductor technology and meeting future demands.

Q 14. Discuss different types of packaging for integrated circuits.

Integrated circuit (IC) packaging protects the delicate die and facilitates connection to external circuits. Packaging choices significantly affect the IC’s performance, cost, and reliability.

- Through-hole Packaging: This traditional method uses leads that pass through holes in the printed circuit board (PCB). Examples include DIP (dual in-line package) and SIP (single in-line package). While cost-effective, this approach is less suitable for high-density applications.

- Surface Mount Technology (SMT): This involves surface-mounted components with leads directly soldered to the PCB surface. SMT packages like QFP (quad flat package), BGA (ball grid array), and CSP (chip scale package) allow for increased density and miniaturization. BGAs provide numerous connections, improving performance, while CSPs minimize size.

- Advanced Packaging: Techniques like system-in-package (SiP), 3D packaging, and chiplets are addressing the challenges of increasing integration and performance. SiP combines multiple ICs into a single package, while 3D packaging stacks dies vertically to increase functionality and reduce footprint. Chiplets allow for modular design, combining specialized dies to create complex systems.

The selection of packaging depends on several factors including the IC’s functionality, performance requirements, cost constraints, and application demands. Advanced packaging technologies are essential for creating high-performance computing systems, smartphones, and other electronics with increasing complexity and miniaturization.

Q 15. What are the common failure mechanisms in electronic devices?

Electronic devices, like any complex system, are prone to various failure mechanisms. These can broadly be categorized into material degradation, process-induced defects, and external factors. Material degradation includes things like electromigration (the movement of metal ions within a conductor due to current flow, leading to open circuits), corrosion (chemical reactions that damage materials), and fatigue (weakening due to repeated stress). Process-induced defects stem from imperfections during manufacturing, such as voids in metallization, contamination, or misalignment of components. External factors include thermal stresses (expansion and contraction due to temperature changes), mechanical shock or vibration, and environmental effects like humidity and electrostatic discharge (ESD).

- Example: A classic example of electromigration is the failure of interconnects in integrated circuits due to high current density. The metal atoms literally migrate, creating voids and eventually breaking the connection.

- Example: Corrosion can occur in devices exposed to moisture, causing the formation of oxides that can disrupt functionality.

Understanding these failure mechanisms is crucial for improving device reliability and extending their lifespan. This involves material selection, process optimization, and robust design techniques.

Career Expert Tips:

- Ace those interviews! Prepare effectively by reviewing the Top 50 Most Common Interview Questions on ResumeGemini.

- Navigate your job search with confidence! Explore a wide range of Career Tips on ResumeGemini. Learn about common challenges and recommendations to overcome them.

- Craft the perfect resume! Master the Art of Resume Writing with ResumeGemini’s guide. Showcase your unique qualifications and achievements effectively.

- Don’t miss out on holiday savings! Build your dream resume with ResumeGemini’s ATS optimized templates.

Q 16. Explain the concept of dielectric breakdown.

Dielectric breakdown is the sudden failure of an insulating material (a dielectric) under a high electric field. Imagine a dielectric as a barrier preventing the flow of current between two conductors. When the applied voltage exceeds the dielectric’s strength, the material’s insulating properties collapse, allowing a large current to flow. This is often destructive, leading to device failure.

This breakdown can occur through two main mechanisms: intrinsic breakdown and extrinsic breakdown. Intrinsic breakdown is a material property related to the dielectric’s inherent ability to withstand high electric fields. It’s like the material reaching a breaking point due to the electric stress. Extrinsic breakdown is caused by flaws within the material such as voids, inclusions, or impurities that act as weak points, lowering the breakdown voltage. Think of it as a crack in a wall – much easier to break than a perfect wall.

Example: A capacitor uses a dielectric material to store electrical energy. If the voltage across the capacitor exceeds the dielectric strength, dielectric breakdown will occur, rendering the capacitor unusable.

Preventing dielectric breakdown involves selecting appropriate dielectrics with high dielectric strength, careful process control to minimize defects, and designing devices with appropriate safety margins.

Q 17. How does temperature affect the performance of electronic devices?

Temperature significantly affects the performance of electronic devices. Increased temperature generally leads to increased carrier mobility in semiconductors (making them conduct better initially), but also accelerates various degradation mechanisms.

- Increased Leakage Current: Higher temperatures increase the thermal energy of electrons, allowing more electrons to overcome the energy barrier and leak across junctions, increasing power consumption and reducing efficiency.

- Reduced Mobility: At very high temperatures, increased lattice vibrations scatter charge carriers, reducing their mobility and thus reducing device speed and performance.

- Material Degradation: High temperatures accelerate chemical reactions and diffusion processes that lead to material degradation, such as oxidation, metal migration, and changes in doping concentration.

- Junction Degradation: Changes in the junction properties of transistors and diodes affect their characteristics, leading to performance degradation.

Example: A smartphone processor will typically throttle its clock speed at high temperatures to prevent overheating and maintain stability. This reduces performance but prevents potential damage.

Thermal management is essential for reliable device operation. This involves techniques like heat sinks, thermal interface materials, and efficient packaging to dissipate heat effectively.

Q 18. Discuss the impact of defects on semiconductor properties.

Defects in semiconductor materials significantly impact their electrical properties. These defects can be point defects (like vacancies or interstitial atoms), line defects (dislocations), or planar defects (grain boundaries). These defects disrupt the crystal lattice and introduce energy levels within the bandgap.

- Impact on Conductivity: Defects can act as scattering centers for charge carriers, reducing their mobility and thus reducing conductivity. Some defects, however, can act as dopants, altering the conductivity type (n-type or p-type).

- Impact on Lifetime: Defects can serve as recombination centers for electrons and holes, reducing the minority carrier lifetime and affecting device performance (especially in solar cells and LEDs).

- Impact on Breakdown Voltage: Defects can weaken the material and lower its breakdown voltage, making it more susceptible to dielectric breakdown.

Example: A dislocation in silicon can act as a non-radiative recombination center in a solar cell, reducing its efficiency by lowering the carrier lifetime and increasing the rate of electron-hole recombination.

Minimizing defects during material growth and processing is crucial for achieving high-quality semiconductor materials with desired properties. Techniques like epitaxial growth, annealing, and gettering are used to reduce the concentration of defects.

Q 19. Explain the principles of photolithography.

Photolithography is a crucial technique in microfabrication used to create patterns on a semiconductor wafer. It’s analogous to printing a circuit onto a tiny silicon chip. The process involves using ultraviolet (UV) light to transfer a pattern from a photomask onto a light-sensitive material (photoresist) coated on the wafer.

The steps are:

- Photoresist Coating: A thin layer of photoresist is spin-coated onto the wafer.

- Exposure: The wafer is exposed to UV light through a photomask, which contains the desired pattern. The light either hardens or softens the photoresist depending on whether it’s a positive or negative resist.

- Development: The exposed photoresist is developed using a solvent, removing either the exposed (positive resist) or unexposed (negative resist) regions.

- Etching: The exposed silicon regions are etched away using chemicals or plasmas, creating the desired pattern.

- Photoresist Removal: The remaining photoresist is removed.

Example: In creating transistors, photolithography is used to define the various layers, such as gate oxides, source/drain regions, and metal interconnects, with each lithography step creating a different layer of the pattern.

Advancements in photolithography such as extreme ultraviolet (EUV) lithography are constantly pushing the boundaries of miniaturization in integrated circuits, allowing for the creation of increasingly smaller and more powerful devices.

Q 20. What are the advantages and disadvantages of different semiconductor materials (e.g., Si, GaAs, GaN)?

Silicon (Si), Gallium Arsenide (GaAs), and Gallium Nitride (GaN) are popular semiconductor materials, each with its own advantages and disadvantages.

| Material | Advantages | Disadvantages |

|---|---|---|

| Silicon (Si) | Abundant, inexpensive, well-established processing technology, high purity readily available. | Relatively low electron mobility compared to GaAs and GaN, indirect bandgap (less efficient light emission). |

| Gallium Arsenide (GaAs) | High electron mobility, direct bandgap (efficient light emission), high-speed applications. | More expensive than Si, more challenging processing technology, less mature technology. |

| Gallium Nitride (GaN) | Very high electron mobility, wide bandgap (high-power, high-temperature operation), high breakdown voltage. | Most expensive, significant challenges in defect control and crystal growth, relatively new technology. |

The choice of material depends on the application. Si is the dominant material for integrated circuits due to its cost-effectiveness and mature technology. GaAs is favored for high-speed electronics and optoelectronics (e.g., lasers and LEDs). GaN is increasingly used in high-power, high-frequency applications like power amplifiers and high-voltage electronics.

Q 21. Describe the working principle of a solar cell.

A solar cell, also known as a photovoltaic cell, converts light energy into electrical energy. The working principle relies on the photovoltaic effect. A typical solar cell is made of a p-n junction, which is a junction between a p-type semiconductor (with holes as majority carriers) and an n-type semiconductor (with electrons as majority carriers).

When sunlight strikes the solar cell, photons (light particles) are absorbed by the semiconductor material. If a photon has sufficient energy (greater than the bandgap energy of the semiconductor), it can excite an electron from the valence band to the conduction band, leaving behind a hole. This creates an electron-hole pair.

Due to the built-in electric field across the p-n junction, the electrons are driven towards the n-side, and the holes towards the p-side. This separation of charges creates a voltage across the junction, and if an external circuit is connected, a current flows, producing electricity.

Example: A typical silicon solar cell uses silicon as the semiconductor material. The absorption of photons in silicon generates electron-hole pairs, leading to the generation of electricity.

The efficiency of a solar cell depends on factors such as the bandgap of the semiconductor, the quality of the p-n junction, and the surface properties of the cell. Material engineering and device design play a significant role in maximizing the efficiency of solar cells.

Q 22. Explain the concept of quantum confinement in nanomaterials.

Quantum confinement in nanomaterials arises when the size of a material is reduced to the nanoscale (typically less than 100 nanometers), leading to the restriction of electron movement. Imagine a bird in a cage: the smaller the cage, the more restricted the bird’s movement. Similarly, in nanomaterials, the electrons are confined within the nanoscale dimensions, altering their energy levels. This confinement dramatically affects the material’s electronic and optical properties.

In bulk materials, electrons can occupy a continuous range of energy levels. However, when the material’s size is reduced to the nanoscale, the energy levels become quantized, meaning they are discrete and separated. This quantization leads to several interesting phenomena, including a shift in the band gap (the energy difference between the valence band and conduction band), enhanced fluorescence, and changes in the material’s conductivity.

Examples: Quantum dots, a type of semiconductor nanocrystal, exhibit size-dependent fluorescence. By controlling the size of the quantum dot, we can tune the emitted wavelength of light. This property finds applications in displays, bioimaging, and solar cells. Quantum wells, another example, are thin layers of semiconductor material sandwiched between other materials. These structures confine electrons in one dimension, leading to improved performance in transistors and lasers.

Q 23. How do you ensure the reliability of electronic devices?

Ensuring the reliability of electronic devices is crucial for their successful operation and longevity. It involves a multi-faceted approach encompassing design, material selection, manufacturing, and testing. Reliability is often quantified using metrics like Mean Time Between Failures (MTBF).

- Robust Design: Designing devices with sufficient safety margins to account for variations in manufacturing and operating conditions. This includes considering thermal effects, voltage fluctuations, and electromagnetic interference (EMI).

- High-Quality Materials: Using materials with inherent stability and resistance to degradation. Careful selection and screening are crucial to avoid defects and impurities.

- Stringent Manufacturing Processes: Implementing strict quality control measures throughout the manufacturing process to minimize defects and inconsistencies. This includes using cleanroom environments, advanced lithography techniques, and rigorous inspection procedures.

- Comprehensive Testing: Conducting thorough testing at various stages of development and manufacturing to identify and eliminate potential weaknesses. This includes environmental stress testing (temperature cycling, humidity testing), electrical testing, and accelerated life testing.

- Redundancy and Fault Tolerance: Incorporating redundant components or employing fault-tolerant designs to enhance the device’s ability to withstand failures without complete system collapse.

For example, in designing a hard drive, we employ error-correcting codes and redundant storage mechanisms to ensure data integrity even in the event of minor component failures. Similarly, aerospace applications demand extremely high reliability, necessitating rigorous testing and the use of highly reliable components.

Q 24. Discuss different techniques for improving the yield of semiconductor manufacturing.

Improving the yield in semiconductor manufacturing, which refers to the percentage of successfully functioning chips produced, is vital for cost reduction and profitability. Several techniques contribute to this:

- Advanced Lithography: Utilizing cutting-edge lithography techniques, like extreme ultraviolet (EUV) lithography, enables the creation of smaller and more complex features on the chip, resulting in higher chip density and potentially reducing defects.

- Process Optimization: Fine-tuning various process parameters such as temperature, pressure, and gas flow during the manufacturing process to enhance the quality and consistency of the fabricated devices.

- Defect Reduction Strategies: Implementing strategies to identify and eliminate sources of defects. This includes using advanced metrology techniques, process monitoring, and statistical process control (SPC).

- Material Improvements: Using higher-quality and more consistent materials can drastically reduce defects and improve yield. This includes careful material selection, purification, and characterization.

- Automation and Robotics: Employing automated and robotic systems reduces human error and enhances process consistency, leading to fewer defects.

- Predictive Modeling and AI: Leveraging advanced modeling and artificial intelligence to predict and prevent potential defects, optimizing the manufacturing process in real-time.

For instance, the adoption of EUV lithography has been crucial in enabling the fabrication of cutting-edge chips with billions of transistors. These improvements in manufacturing techniques translate directly into higher yields and lower costs per chip.

Q 25. Describe different types of memory devices and their operating principles.

Memory devices are essential components in electronic systems, enabling the storage and retrieval of data. They are broadly classified into several types, each with unique operating principles:

- Random Access Memory (RAM): RAM is volatile memory, meaning it loses data when power is lost. It offers fast read and write speeds, making it ideal for active data storage during system operation. Types include Static RAM (SRAM), which uses flip-flops to store data, and Dynamic RAM (DRAM), which stores data as electrical charges in capacitors.

- Read-Only Memory (ROM): ROM is non-volatile memory, retaining data even when power is off. It is typically used for storing firmware or boot instructions. Variations include Programmable ROM (PROM), Erasable PROM (EPROM), and Electrically Erasable PROM (EEPROM).

- Flash Memory: Flash memory is a non-volatile memory type that offers a balance between storage capacity, speed, and cost-effectiveness. It’s commonly used in USB drives, SSDs, and embedded systems. There are two main types: NAND flash and NOR flash, differing in their architecture and access methods.

- Magnetic Memory: This older type of memory uses magnetic domains to store data. Hard disk drives (HDDs) are a common example, utilizing rotating platters with magnetic coatings.

The operating principles vary across these types, involving different physical mechanisms for storing and retrieving data. For example, DRAM uses tiny capacitors to store charge, while flash memory uses floating-gate transistors to trap electrons. Understanding these mechanisms is crucial for selecting the appropriate memory technology for a particular application.

Q 26. Explain the concept of CMOS technology.

Complementary Metal-Oxide-Semiconductor (CMOS) technology is the dominant technology used in modern integrated circuits (ICs). It’s a type of metal-oxide-semiconductor field-effect transistor (MOSFET) technology that uses both p-type and n-type MOSFETs in a complementary configuration. This complementary arrangement offers several key advantages.

In a CMOS circuit, one transistor is a p-type MOSFET (PMOS) and the other is an n-type MOSFET (NMOS). These transistors are arranged in such a way that only one transistor is conducting at any given time, minimizing power consumption. This is a significant advantage over older technologies, contributing to the efficiency of modern electronics.

Operation: CMOS circuits rely on the switching behavior of MOSFETs. By controlling the voltage applied to the gate of the MOSFETs, we can switch them between the ‘on’ and ‘off’ states, controlling the flow of current. The complementary arrangement ensures that only one transistor conducts at a time, drastically reducing the power dissipation. The low power consumption is a primary reason for CMOS’s widespread adoption.

CMOS technology has been instrumental in the miniaturization and increased performance of integrated circuits. The continuous scaling down of CMOS transistors has led to the exponential growth in computing power over the past several decades.

Q 27. What are the challenges associated with integrating new materials into existing semiconductor processes?

Integrating new materials into existing semiconductor processes presents numerous challenges. Semiconductor manufacturing is a highly refined and complex process, and introducing new materials requires careful consideration of several factors:

- Material Compatibility: The new material must be compatible with existing materials and processes in the fabrication flow. This includes considerations of thermal stability, chemical compatibility, and lattice matching.

- Process Integration: Adapting the existing fabrication processes to accommodate the new material. This might require modifying existing equipment or developing new processing steps.

- Defect Control: Minimizing defects introduced by the new material. This necessitates careful control of the material’s purity, deposition methods, and subsequent processing steps.

- Cost and Scalability: The cost of the new material and the scalability of its production must be considered to ensure economic viability.

- Performance Optimization: Ensuring that the integration of the new material results in improved device performance, rather than degrading it.

- Reliability and Longevity: Evaluating the long-term reliability and stability of the devices incorporating the new material, including considerations of ageing effects.

For example, integrating new high-k dielectric materials into CMOS transistors required significant advancements in deposition and etching techniques to maintain the required quality and reliability. Similarly, the incorporation of novel 2D materials like graphene into semiconductor devices faces challenges in terms of material quality, integration with silicon-based processes, and achieving desired device characteristics.

Q 28. Describe the role of advanced packaging in improving device performance.

Advanced packaging plays a crucial role in improving device performance and enabling new functionalities. It goes beyond simply connecting chips together; it involves sophisticated techniques to enhance electrical performance, thermal management, and system integration.

- Higher Density Interconnects: Advanced packaging techniques enable higher density interconnects, allowing for increased communication bandwidth between chips and improved system performance.

- Improved Thermal Management: Packaging solutions incorporate thermal vias and heat sinks to effectively dissipate heat, preventing overheating and increasing device reliability, particularly for high-power applications.

- System-in-Package (SiP): SiP integrates multiple components, including passive components, into a single package, reducing size, cost, and improving functionality.

- 3D Packaging: 3D stacking allows for the vertical integration of multiple chips, significantly increasing the chip density and overall system performance. This is particularly important for high-performance computing and memory-intensive applications.

- Heterogeneous Integration: Integrating different types of chips with distinct functionalities within a single package to create more powerful and versatile systems.

For instance, advanced packaging is crucial for high-end graphics cards, where multiple GPUs are stacked to improve parallel processing capabilities. Similarly, in mobile devices, advanced packaging allows for integrating multiple chips with different functions, like processors, memory, and sensors, into a compact and energy-efficient package.

Key Topics to Learn for Electronic Materials and Devices Interview

- Semiconductor Physics: Understanding band theory, doping, carrier transport mechanisms (drift and diffusion), and p-n junctions is fundamental. Consider exploring different semiconductor materials and their properties.

- Device Fabrication Techniques: Familiarize yourself with common methods like photolithography, etching, deposition (e.g., CVD, sputtering), and doping processes. Understanding the trade-offs between different techniques is crucial.

- MOSFETs and other transistors: Deeply understand the operation, characteristics, and limitations of MOSFETs (nMOS, pMOS). Explore other transistor types like bipolar junction transistors (BJTs) and their applications.

- Materials Characterization: Learn about techniques used to analyze electronic materials, such as X-ray diffraction (XRD), scanning electron microscopy (SEM), and transmission electron microscopy (TEM). Understanding how these techniques provide insights into material properties is valuable.

- Device Modeling and Simulation: Familiarity with simulation tools (e.g., SPICE) and their application in predicting device behavior and optimizing designs is highly advantageous.

- Emerging Materials and Devices: Stay updated on advancements in materials like 2D materials (graphene, MoS2), and novel device architectures. Demonstrating awareness of cutting-edge research shows initiative.

- Practical Applications: Relate theoretical concepts to real-world applications. For example, discuss how specific materials and device structures are used in integrated circuits, sensors, solar cells, or LEDs.

- Problem-Solving Approach: Practice analyzing device characteristics, identifying failure mechanisms, and proposing solutions to common challenges in electronic device design and fabrication.

Next Steps

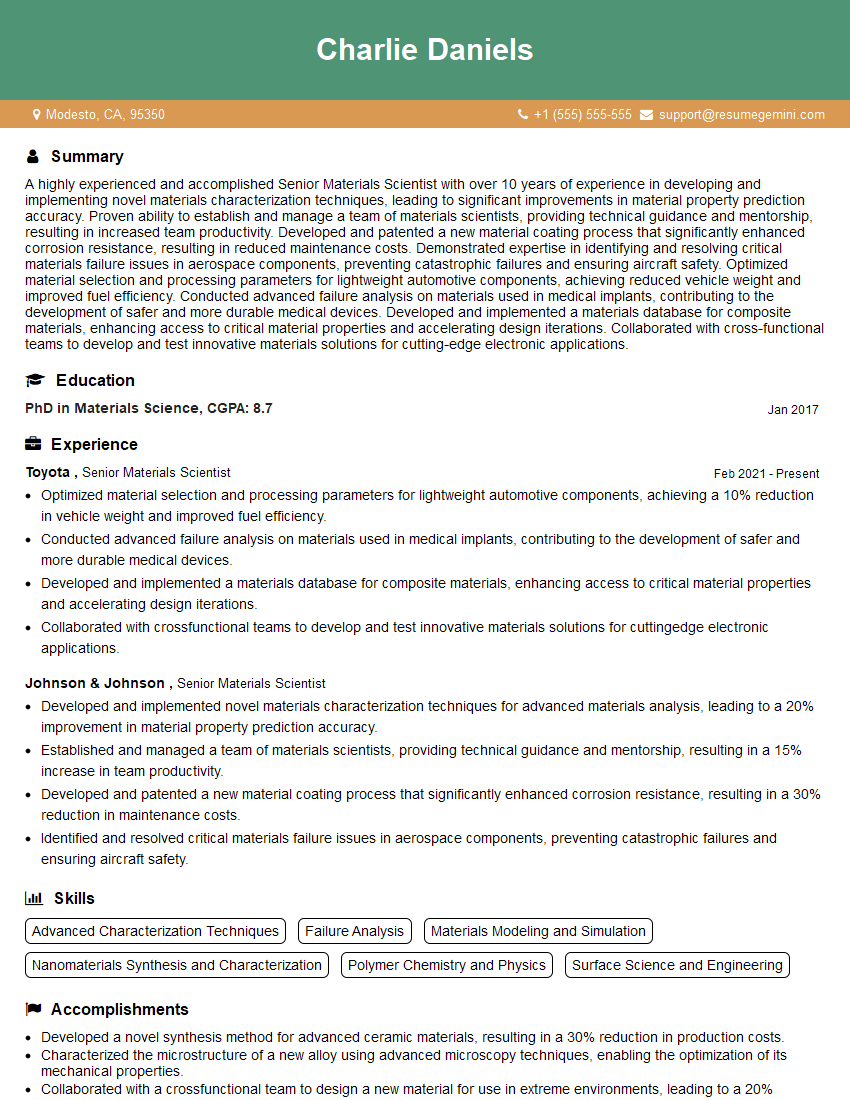

Mastering Electronic Materials and Devices opens doors to exciting career opportunities in research, development, and manufacturing within the semiconductor industry and related fields. A strong understanding of these concepts significantly enhances your marketability. To maximize your chances of securing your dream role, it’s vital to present your skills and experience effectively. Creating an ATS-friendly resume is key to getting your application noticed by recruiters. We strongly encourage you to leverage ResumeGemini as your trusted resource for building a professional and impactful resume. ResumeGemini provides examples of resumes tailored specifically to Electronic Materials and Devices roles to help guide you. Take advantage of these resources to present yourself confidently and land your ideal position.

Explore more articles

Users Rating of Our Blogs

Share Your Experience

We value your feedback! Please rate our content and share your thoughts (optional).

What Readers Say About Our Blog

To the interviewgemini.com Webmaster.

Very helpful and content specific questions to help prepare me for my interview!

Thank you

To the interviewgemini.com Webmaster.

This was kind of a unique content I found around the specialized skills. Very helpful questions and good detailed answers.

Very Helpful blog, thank you Interviewgemini team.